week9

Program에는 Instruction이 있고 이 Instruction은 ISA에 있는 명령어 집합 중에 하나임 따라서 ISA에는 이 명령어에 따른 지침도 들어있음

이걸 가변길이로 하느냐 아니면 고정길이로 하느냐에 따라 CISC, RISC로 나뉜다.

Instruction의 길이를 가변길이(CISC) 고정길이(RISC)

CISC(가변길이)

명령어는 복잡하지만 개수는줄인다.

한 개의 명령어로 여러 작업을 수행

다양한 주소 지정방식

단점: 파이프라이닝 비효율적

RISC(고정길이)

명령어는 단순하게 대신 빠르고 많이 처리

연산은 오직 레지스터 간에 수행

파이프라이닝과 병렬 처리에 최적화

장점:실행속도가 빠름

단점:코드 길이가 길어질 수 있음(복잡한 연산은 여러 명령어로 나눠야 해서)

Immediate: 바로 대입

Direct: 바로 Operand가 저장되어있는 메모리 주소를 지정

Indirect:포인터를 지정

명령어 가져오기(Fetch)

PC(현재 실행할 명령어의 주소를 보관)

AR(메모리에 접근 할 때 주소를 보관)

IR(메모리에서 읽어온 명령어 코드를 보관)=실행중인 명령어 저장

명령어 해독(Decode)

IR(명령어의 오퍼코드와 주소 부분을 분리해서 해석)

AR(명령어에서 추출한 오퍼랜드의 주소를 저장)

명령어 실행(Execute)

DR(메모리에서 읽어온 오퍼랜드 데이터 보관)

(ALU에서 계산하거나 AC로 전달)

->AC(연산 결과나 중간 데이터를 저장)

->TR(계산 중 발생하는 임시 값 저장)

DR,AC,IR,TR은 16비트

AR,PC는 12비트 왜냐면 메모리 주소를 갖고 있어야하므로

->상위 4비트는 0으로 채워져 16비트로 맞춘다.

버스->AR/PC 버스에서 하위 12비트만 해당 레지스터로 복사(왜냐면 상위 4비트는 0으로 채워져있으니)

INPR,OUTR:버스의 8개 최하위 비트와 통신

INPR: 입력 장치(키보드 등)에서 문자를 수신한 후 이를 AC로 전송

OUTR: AC로부터 문자를 수신하고 그것을 출력 장치로 전달

LD:버스에서 레지스터로 데이터 로드

INR:레지스터 값을 1 증가

CLR:레지스터 값을 0으로 초기화

레지스터는 단순 저장소가 아니라 이진 카운터 역할도 수행

병렬 로드(parallel load):여러 비트를 한 번에 입력받음

동기식 클리어(synchronous clear): 클럭 신호와 함께 클리어 작동

DR<-AC and AC<-DR (Exchanged)

이 두 과정은 한 번에 발생하여 swap처럼 실행될 수 있는데 여기서 DR<-AC는 DR<-BUS<-AC 이고 AC<-DR은 AC<-ALU<-DR이다. 따라서 서로 다른 선을 타므로 가능한 것이다.

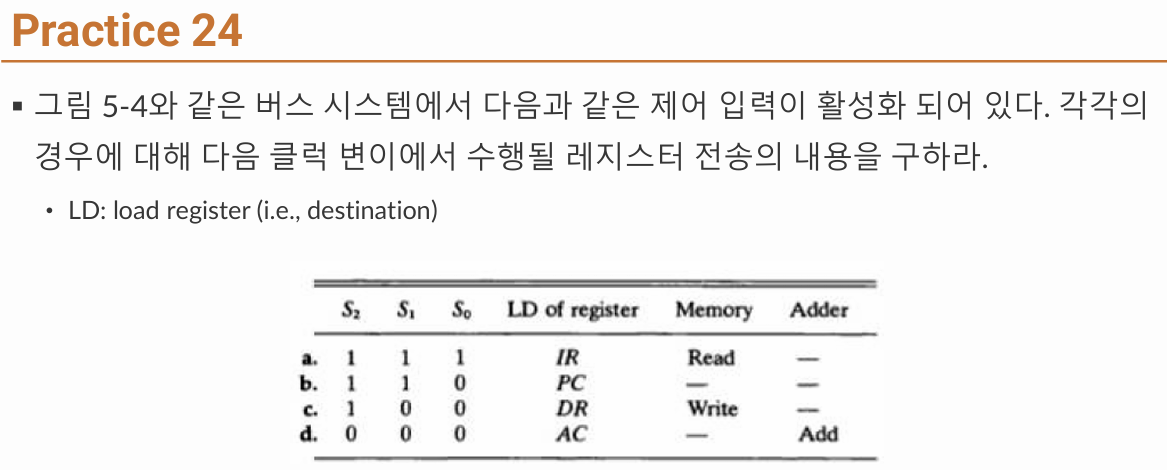

a.IR<-M[AR]

b.PC<-TR

c.DR<-AC/ AC<-ALU<-DR(Exchanged)

d.AC<AC+DR

마스터 Clock이 있어야 레지스터가 작동하고 메모리를 저장하고 그러는 것

Intruction 주기

1. 메모리로부터 Instruction을 가져옴

2. Instruction을 해석

3. 만약 instruction이 간접주소를 갖고 있으면 메모리로부터 실제 주소를 가져옴

4. instruction을 실행

(HALT만나기 전까지 cycle 반복)

FETCH의 과정

T0일때 PC의 값을 AR에 저장

T1일때 T0에서 저장한 AR을 활용해서 IR에 M[AR]을 저장하고 PC를 1증가 시킴

T2일때 D0, ... , D7<-IR(12-14)을 저장하고 AR<-IR(0-11), I<-IR(15)를 저장

이걸로 이해하면 됨

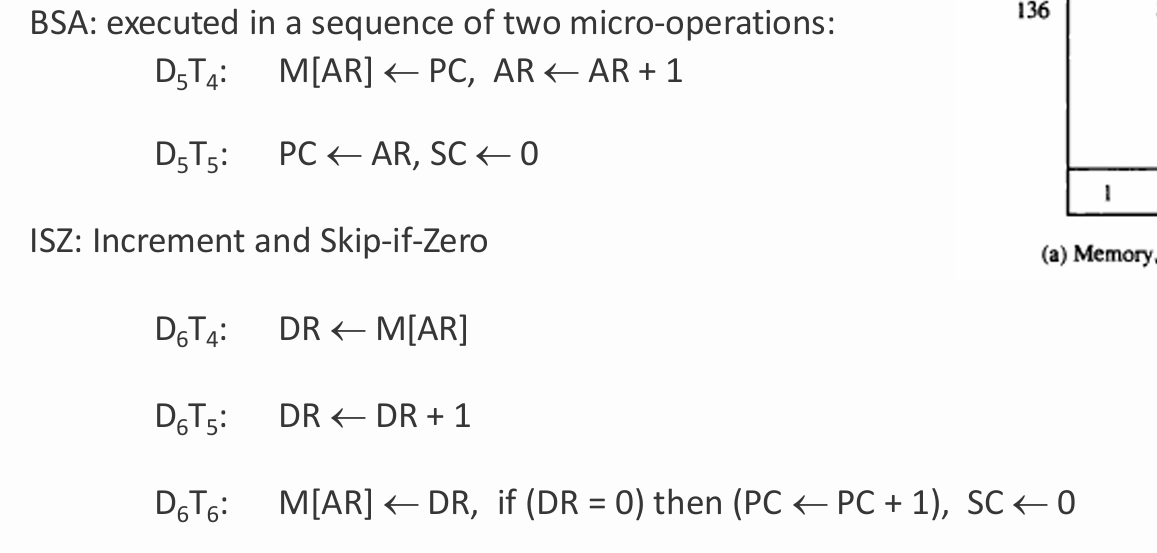

M[AR]은 무조건 DR에 저장해야한다.

그리고 마지막에 SC<-0 꼭 하기

FGI(입력 작업을 제어하기 위한 1비트 입력 플래그 정보가 있으면 1, 컴퓨터가 수용 가능하면 0)

FGO(출력 작업을 제어하기 위한 1비트 출력 플래그 컴퓨터가 정보를 보낼 수 있으면 1, 0이면 보낼 수 없으니 출력장치가 기다려야함)

(당연한 얘기)

1. 초기 FGI는 0으로 설정(입력을 받기 위해서)

2. 입력(8비트 alpanumeric code)가 들어오면 FGI가 1로 설정됨

3. 이미 설정된 데이터는 다른 데이터 입력에 의해 변경이 될 수 없음

4. 컴퓨터가 플래그 비트를 검사하고 1이면 INPR로부터 정보를 AC에 전달하고 FGI는 0으로 변경됨

5. 플래그비트가 0이 되었을 때 입력장치로부터 입력이 들어오면 INPR이 변경될 수 있음

FGO는 생략

왜냐면 위랑 유사함

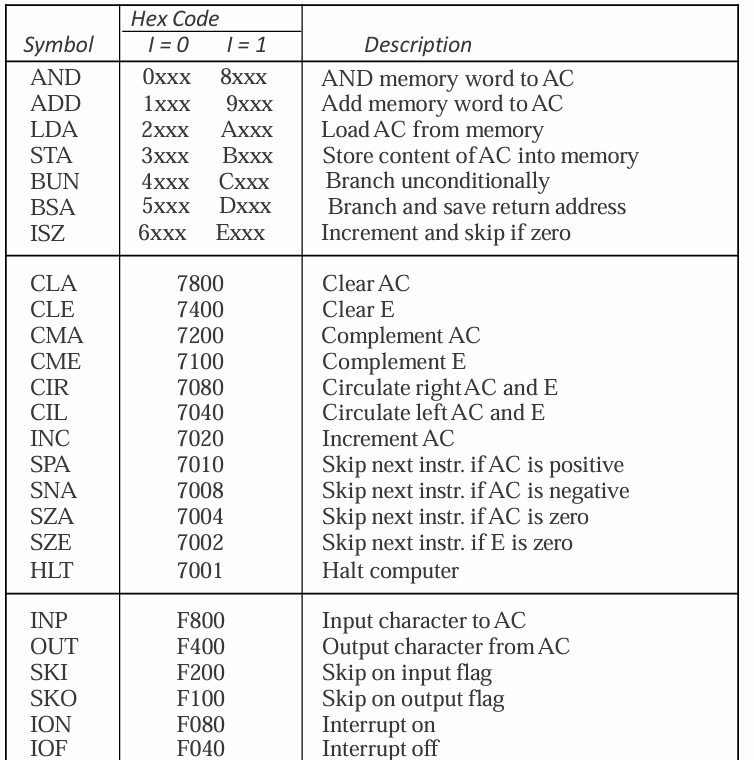

INP:입력 버퍼(INPR)

->누산기(AC) 하위 8비트<-INPR, 입력 완료 플래그 클리어

OUT:출력

OUTR<-누산기 하위 8비트, 출력 완료 플래그 클리어

SKI

입력 완료 상태면 다음 명령어 건너뜀

SKO

출력 완료 상태면 다음 명령어 건너뜀

ION

인터럽트 허용 활성화

IOF

인터럽트 허용 비활성화

32비트의 256K 워드를 메모리로 가진 컴퓨터에서 하나의 이진 명령어 코드는 한 메모리에 저장된다.

-> 32비트(전체 비트 수를 뜻 함)

->256K워드를 메모리로 가짐 18비트 (주소 부분)

명령은 간접비트, 연산코드, 64개 레지스터 중 하나를 지시하는 레지스터 코드 부분, 주소 부분으로 구성된다.

->간접비트는 1비트(약속)

->연산코드는 따로 얘기가 없음(연산코드 비트=전체 비트 - 주소부분 비트 - 간접비트- 레지스터 코드 부분 비트 로 구함)

->레지스터 코드 부분 64개 레지스터 중 하나를 지시해야 하므로 6비트임

따라서 연산 코드 비트 수= 32-18-1-6=7비트임

따라서

1. 연산 코드: 7비트 레지스터 코드 부분: 6비트 , 주소 부분의 비트: 18비트

2.

| 간접비트(1bit) | 연산코드(7bit) | 레지스터 코드 비트(6bit) | 주소비트(18bit) |

| bit 31 | 30~24 | 23~18 | 17~0 |

3. 주소:18비트

데이터:32비트(전체코드)